January 2006

## ARINC 429 SERIAL TRANSMITTER AND DUAL RECEIVER

### **GENERAL DESCRIPTION**

The HI-8282A is a silicon gate CMOS device for interfacing the ARINC 429 serial data bus to a 16-bit parallel data bus. Two receivers and an independent transmitter are provided. The receiver input circuitry and logic are designed to meet the ARINC 429 specifications for loading, level detection, timing, and protocol. The transmitter section provides the ARINC 429 communication protocol. Additional interface circuitry such as the Holt HI-8585, HI-8586 or HI-3182 is required to translate the 5 volt logic outputs to ARINC 429 drive levels.

The 16-bit parallel data bus exchanges the 32-bit ARINC data word in two steps when either loading the transmitter or interrogating the receivers. The data bus interfaces with CMOS and TTL.

Timing of all the circuitry begins with the master clock input, CLK. For ARINC 429 applications, the master clock frequency is 1 MHz.

Each independent receiver monitors the data stream with a sampling rate 10 times the data rate. The sampling rate is software selectable at either 1MHz or 125KHz. The results of a parity check are available as the 32nd ARINC bit. The HI-8282A examines the null and data timings and will reject erroneous patterns. For example, with a 125 KHz clock selection, the data frequency must be between 10.4 KHz and 15.6 KHz.

The transmitter has a First In, First Out (FIFO) memory to store 8 ARINC words for transmission. The data rate of the transmitter is software selectable by dividing the master clock, CLK, by either 10 or 80. The master clock is used to set the timing of the ARINC transmission within the required resolution.

## **APPLICATIONS**

- Avionics data communication

- Serial to parallel conversion

- Parallel to serial conversion

### **FEATURES**

- ARINC specification 429 compliant

- Alternate source to Intersil HS-3282 in all ARINC 429 applications

- Small footprint 44-pin QFP package option

- 16-Bit parallel data bus

- Direct receiver interface to ARINC bus

- Timing control 10 times the data rate

- Selectable data clocks

- Automatic transmitter data timing

- 8 word transmit FIFO

- Receiver error rejection per ARINC specification 429

- Self test mode

- Parity functions

- Low power, single 5 volt supply

- Industrial & full military temperature ranges

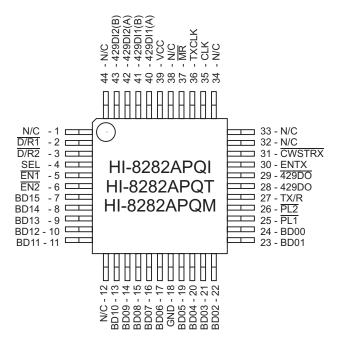

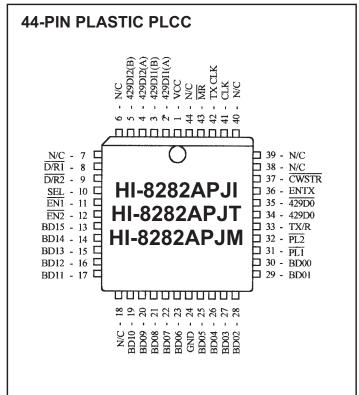

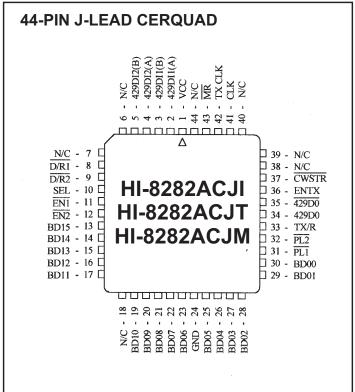

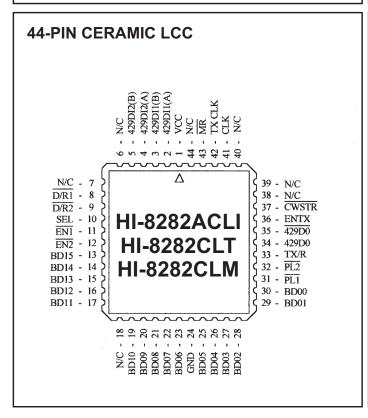

# PIN CONFIGURATION (Top View)

44-Pin Plastic Quad Flat Pack (PQFP)

(See page 10 for additional Package Pin Configurations)

# **PIN DESCRIPTION**

| SYMBOL     | FUNCTION | DESCRIPTION                                                                                                     |  |  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| VCC        | POWER    | +5V ±5%                                                                                                         |  |  |  |

| 429DI1 (A) | INPUT    | ARINC receiver 1 positive input                                                                                 |  |  |  |

| 429DI1 (B) | INPUT    | ARINC receiver 1 negative input                                                                                 |  |  |  |

| 429DI2 (A) | INPUT    | ARINC receiver 2 positive input                                                                                 |  |  |  |

| 429DI2 (B) | INPUT    | ARINC receiver 2 negative input                                                                                 |  |  |  |

| D/R1       | OUTPUT   | Receiver 1 data ready flag                                                                                      |  |  |  |

| D/R2       | OUTPUT   | Receiver 2 data ready flag                                                                                      |  |  |  |

| SEL        | INPUT    | Receiver data byte selection (0 = BYTE 1) (1 = BYTE 2)                                                          |  |  |  |

| EN1        | INPUT    | Data Bus control, enables receiver 1 data to outputs                                                            |  |  |  |

| EN2        | INPUT    | Data Bus control, enables receiver 2 data to outputs if EN1 is high                                             |  |  |  |

| BD15       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD14       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD13       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD12       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD11       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD10       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD09       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD08       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD07       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD06       | I/O      | Data Bus                                                                                                        |  |  |  |

| GND        | POWER    | 0 V                                                                                                             |  |  |  |

| BD05       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD04       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD03       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD02       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD01       | I/O      | Data Bus                                                                                                        |  |  |  |

| BD00       | I/O      | Data Bus                                                                                                        |  |  |  |

| PL1        | INPUT    | Latch enable for byte 1 entered from data bus to transmitter FIFO.                                              |  |  |  |

| PL2        | INPUT    | Latch enable for byte 2 entered from data bus to transmitter FIFO. Must follow PL1.                             |  |  |  |

| TX/R       | OUTPUT   | Transmitter ready flag. Goes low when ARINC word loaded into FIFO. Goes high after transmission and FIFO empty. |  |  |  |

| 429DO      | OUTPUT   | "ONES" data output from transmitter.                                                                            |  |  |  |

| 429DO      | OUTPUT   | "ZEROES" data output from transmitter.                                                                          |  |  |  |

| ENTX       | INPUT    | Enable Transmission                                                                                             |  |  |  |

| CWSTR      | INPUT    | Clock for control word register                                                                                 |  |  |  |

| CLK        | INPUT    | Master Clock input                                                                                              |  |  |  |

| TX CLK     | OUTPUT   | Transmitter Clock equal to Master Clock (CLK), divided by either 10 or 80.                                      |  |  |  |

| MR         | INPUT    | Master Reset, active low                                                                                        |  |  |  |

## **FUNCTIONAL DESCRIPTION**

#### **CONTROL WORD REGISTER**

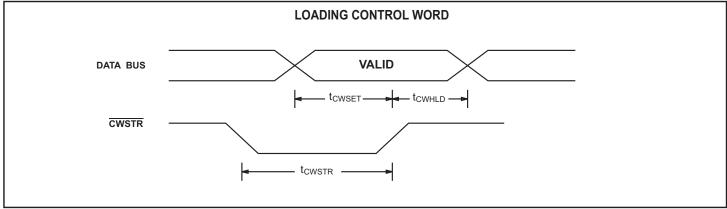

The HI-8282A contains 10 data flip flops whose D inputs are connected to the data bus and clocks connected to CWSTR. Each flip flop provides options to the user as follows:

| DATA<br>BUS<br>PIN | FUNCTION                           | CONTROL            | DESCRIPTION                                                                                            |

|--------------------|------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|

| BDO5               | SELF TEST                          | 0 = ENABLE         | If enabled, an internal connection is made passing 429DO and 429DO to the receiver logic inputs        |

| BDO6               | RECEIVER 1<br>DECODER              | 1 = ENABLE         | If enabled, ARINC bits 9 and,<br>10 must match the next two<br>control word bits                       |

| BDO7               | -                                  | -                  | If Receiver 1 Decoder is enabled, the ARINC bit 9 must match this bit                                  |

| BDO8               | -                                  | -                  | If Receiver 1 Decoder is<br>enabled, the ARINC bit 10<br>must match this bit                           |

| BDO9               | RECEIVER 2<br>DECODER              | 1 = ENABLE         | If enabled, ARINC bits 9 and<br>10 must match the next two<br>control word bits                        |

| BD10               | -                                  | -                  | If Receiver 2 Decoder is enabled, then ARINC bit 9 must match this bit                                 |

| BD11               | -                                  | -                  | If Receiver 2 Decoder is enabled, then ARINC bit 10 must match this bit                                |

| BD12               | INVERT<br>XMTR<br>PARITY           | 1 = ENABLE         | Logic 0 enables normal odd parity<br>and Logic 1 enables even parity<br>output in transmitter 32nd bit |

| BD13               | XMTR DATA 0 = ÷1 CLK SELECT 1 = ÷8 |                    | CLK is divided either by 10 or 80 to obtain XMTR data clock                                            |

| BD14               | RCVR DTA<br>CLK SELECT             | 0 = ÷10<br>1 = ÷80 | CLK is divided either by 10 or<br>80 to obtain RCVR data clock                                         |

#### **ARINC 429 DATA FORMAT**

The following table shows the bit positions in exchanging data with the receiver or the transmitter. ARINC bit 1 is the first bit transmitted or received.

|              | BYTE 1   |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| DATA<br>BUS  | BD<br>15 | BD<br>14 | BD<br>13 | BD<br>12 | BD<br>11 | BD<br>10 | BD<br>09 | BD<br>08 | BD<br>07 | BD<br>06 | BD<br>05 | BD<br>04 | BD<br>03 | BD<br>02 | BD<br>01 | BD<br>00 |

| ARINC<br>BIT | 13       | 12       | 11       | 10       | 9        | 31       | 30       | 32       | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        |

| BYTE 2       |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| DATA<br>BUS  | BD<br>15 | BD<br>14 | BD<br>13 | BD<br>12 | BD<br>11 | BD<br>10 | BD<br>09 | BD<br>08 | BD<br>07 | BD<br>06 | BD<br>05 | BD<br>04 | BD<br>03 | BD<br>02 | BD<br>01 | BD<br>00 |

| ARINC<br>BIT | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       | 15       | 14       |

#### THE RECEIVERS

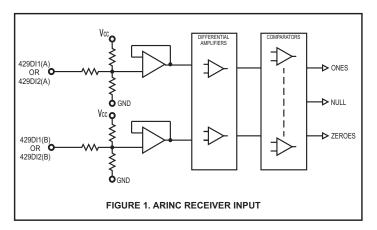

#### **ARINC BUS INTERFACE**

Figure 1 shows the input circuit for each receiver. The ARINC 429 specification requires the following detection levels:

| <u>AGE</u> |

|------------|

| olts       |

| olts       |

| olts       |

|            |

The HI-8282A guarantees recognition of these levels with a common mode Voltage with respect to GND less than ±5V for the worst case condition (4.75V supply and 13v signal level).

The tolerances in the design guarantee detection of the above levels, so the actual acceptance ranges are slightly larger. If the ARINC signal is out of the actual acceptance ranges, including the nulls, the chip rejects the data.

### HI-8282A-10

The HI-8282A-10 option is similar to the HI-8282A with the exception that it allows an external 10 Kohm resistor to be added in series with each ARINC input without affecting the ARINC input thresholds. This option is especially useful in applications where lightning protection circuitry is also required.

Each side of the ARINC bus must be connected through a 10 Kohm series resistor in order for the chip to detect the correct ARINC levels. The typical 10 volt differential signal is translated and input to a window comparator and latch. The comparator levels are set so that with the external 10 Kohm resistors, they are just below the standard 6.5 V minimum ARINC data threshold and just above the 2.5 V maximum ARINC null threshold.

The receivers of the HI-8282A-10 when used with external 10 Kohm resistors will withstand DO-160D, Level 3, waveforms 3, 4 and 5A. No additional lightning protection circuit is necessary.

Please refer to the Holt AN-300 Application Note for additional information and recommendations on lightning protection of Holt Line Drivers and Receivers.

## **FUNCTIONAL DESCRIPTION (cont.)**

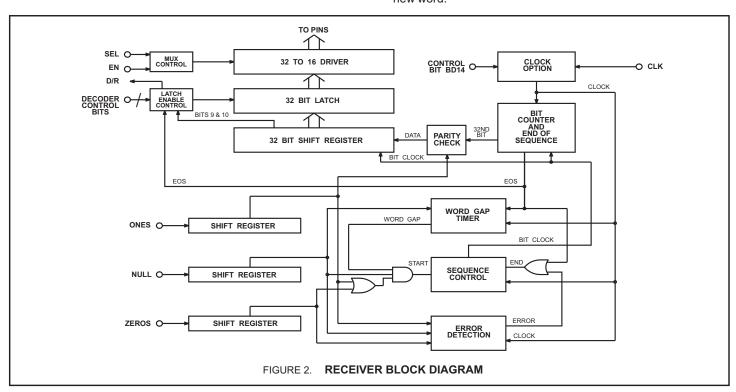

#### RECEIVER LOGIC OPERATION

Figure 2 shows a block diagram of the logic section of each receiver.

#### **BIT TIMING**

The ARINC 429 specification contains the following timing specification for the received data:

|                        | <u>HIGH SPEED</u>      | LOW SPEED         |

|------------------------|------------------------|-------------------|

| BIT RATE               | 100K BPS ± 1%          | 12K -14.5K BPS    |

| <b>PULSE RISE TIME</b> | $1.5 \pm 0.5  \mu sec$ | 10 ± 5 μsec       |

| <b>PULSE FALL TIME</b> | 1.5 ± 0.5 µsec         | 10 ± 5 µsec       |

| PULSE WIDTH            | 5 µsec ± 5%            | 34.5 to 41.7 µsec |

The HI-8282A accepts signals that meet these specifications and rejects outside the tolerances. The way the logic operation achieves this is described below:

- Key to the performance of the timing checking logic is an accurate 1MHz clock source. Less than 0.1% error is recommended.

- 2. The sampling shift registers are 10 bits long and must show three consecutive Ones, Zeros or Nulls to be considered valid data. Additionally, for data bits, the One or Zero in the upper bits of the sampling shift registers must be followed by a Null in the lower bits within the data bit time. For a Null in the word gap, three consecutive Nulls must be found in both the upper and lower bits of the sampling shift register. In this manner the minimum pulse width is guaranteed.

3. Each data bit must follow its predecessor by not less than 8 samples and no more than 12 samples. In this manner the bit rate is checked. With exactly 1MHz input clock frequency, the acceptable data bit rates are as follows:

|                   | <u>HIGH SPEED</u> | LOW SPEED |

|-------------------|-------------------|-----------|

| DATA BIT RATE MIN | 83K BPS           | 10.4K BPS |

| DATA BIT RATE MAX | 125K BPS          | 15.6K BPS |

4. The Word Gap timer samples the Null shift register every 10 input clocks (80 for low speed) after the last data bit of a valid reception. If the Null is present, the Word Gap counter is incremented. A count of 3 will enable the next reception.

#### **RECEIVER PARITY**

The receiver parity circuit counts Ones received, including the parity bit, ARINC bit 32. If the result is odd, then "0" will appear in the 32nd bit.

#### **RETRIEVING DATA**

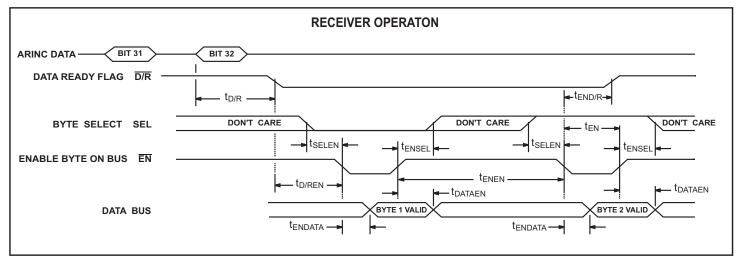

Once 32 valid bits are recognized, the receiver logic generates an End of Sequence (EOS). If the receiver decoder is enabled and the 9th and 10th ARINC bits match the control word program bits or if the receiver decoder is disabled, then EOS clocks the data ready flag flip flop to a "1",  $\overline{D/R1}$  or  $\overline{D/R2}$  (or both) will go low. The data flag for a receiver will remain low until after both ARINC bytes from that receiver are retrieved. This is accomplished by activating  $\overline{EN}$  with SEL, the byte selector, low to retrieve the first byte and activating  $\overline{EN}$  with SEL high to retrieve the second byte.  $\overline{EN1}$  retrieves data from receiver 1 and  $\overline{EN2}$  retrieves data from receiver 2.

If another ARINC word is received and a new EOS occurs before the two bytes are retrieved, the data is overwritten by the new word.

## **FUNCTIONAL DESCRIPTION (cont.)**

#### **TRANSMITTER**

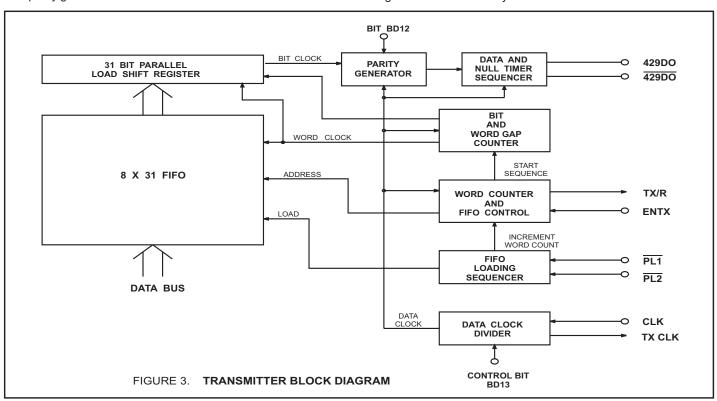

A block diagram of the transmitter section is shown in Figure 3.

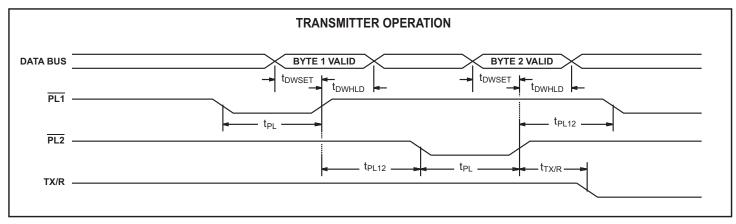

#### FIFO OPERATION

The FIFO is loaded sequentially by first pulsing PL1 to load byte 1 and then PL2 to load byte 2. The control logic automatically loads the 31 bit word in the next available position of the FIFO. If TX/R, the transmitter ready flag, is high (FIFO empty), then 8 words, each 31 bits long, may be loaded. If TX/R is low, then only the available positions may be loaded. If all 8 positions are full, the FIFO ignores further attempts to load data.

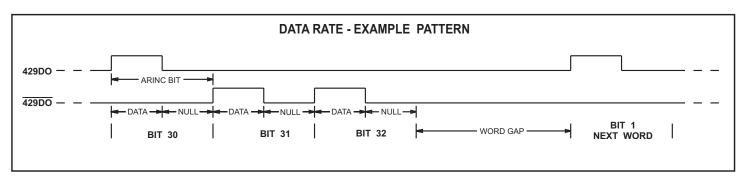

#### **DATA TRANSMISSION**

When ENTX goes high, enabling transmission, the FIFO positions are incremented with the top register loading into the data transmission shift register. Within 2.5 data clocks the first data bit appears at either 429DO or 429DO. The 31 bits in the data transmission shift register are presented sequentially to the outputs in the ARINC 429 format with the following timing:

|                     | HIGH SPEED | LOW SPEED  |

|---------------------|------------|------------|

| ARINC DATA BIT TIME | 10 Clocks  | 80 Clocks  |

| DATA BIT TIME       | 5 Clocks   | 40 Clocks  |

| NULLBITTIME         | 5 Clocks   | 40 Clocks  |

| WORD GAPTIME        | 40 Clocks  | 320 Clocks |

.........

The word counter detects when all loaded positions are transmitted and sets the transmitter ready flag, TX/R, high.

#### TRANSMITTER PARITY

The parity generator counts the ONES in the 31-bit word. If the

BD12 control word bit is set low, the 32nd bit transmitted will make parity odd. If the control bit is high, the parity is even.

#### **SELF TEST**

If the BD05 control word bit is set low, 429DO or  $\overline{429DO}$  are internally connected to the receivers inputs, bypassing the interface circuitry. Data to Receiver 1 is as transmitted and data to Recevier 2 is the complement. 429DO and  $\overline{429DO}$  outputs remain active during self test.

#### SYSTEM OPERATION

The two receivers are independent of the transmitter. Therefore, control of data exchanges is strictly at the option of the user. The only restrictions are:

- 1. The received data may be overwritten if not retrieved within one ARINC word cycle.

- 2. The FIFO can store 8 words maximum and ignores attempts to load addition data if full.

- 3. Byte 1 of the transmitter data must be loaded first.

- 4. Either byte of the received data may be retrieved first. Both bytes must be retrieved to clear the data ready flag.

- 5. After ENTX, transmission enable, goes high it cannot go low until TX/R, transmitter ready flag, goes high. Otherwise, one ARINC word is lost during transmission.

### MASTER RESET (MR)

On a Master Reset data transmission and reception are immediately terminated, the transmit FIFO and receivers cleared as are the transmit and receive flags. The Control Register is not affected by a Master Reset.

## **FUNCTIONAL DESCRIPTION (cont.)**

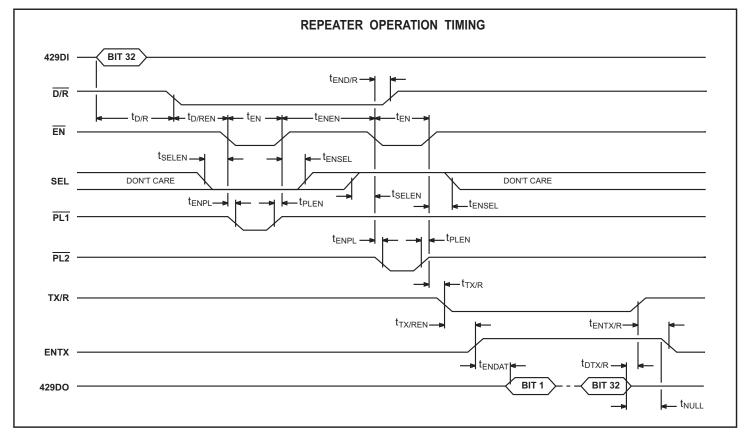

#### REPEATER OPERATION

The repeater mode of operation allows a data word that has been received by the HI-8282A to be placed directly into its FIFO for transmission. After a 32-bit word has been shifted into the receiver shift register, the  $\overline{D/R}$  flag will go low. A logic "0" is placed on the SEL line and  $\overline{EN}$  is strobed. This is the same procedure as for normal receiver operation and it places the lower byte (16) of the data word on the data bus. By strobing  $\overline{PL1}$  at the same time as  $\overline{EN}$ ,

the byte will also be placed into the transmitter FIFO. SEL is then taken high and  $\overline{\text{EN}}$  is strobed again to place the upper byte of the data word on the data bus. By strobing  $\overline{\text{PL2}}$  at the same time as  $\overline{\text{EN}}$ , the second byte will also be placed into the FIFO. The data word is now ready to be transmitted according to the parity programmed into the control word register.

In normal operation, either byte of a received data word may be read from the receiver latches first by use of SEL input. During repeater operation however, the lower byte of the data word must be read first. This is necessary because, as the data is being read, it is also being loaded into the FIFO and the transmitter FIFO is always loaded with the lower byte of the data word first.

## **TIMING DIAGRAMS**

# **TIMING DIAGRAMS (cont.)**

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage Vcc · · · · · · · -0.3V to +7V           | Power Dissipation · · · · · 500mW                                |

|---------------------------------------------------------|------------------------------------------------------------------|

| Voltage at ARINC Inputs · · · · · -29V to +29V          | Operating Temperature Range: (Industrial) · · · · -40°C to +85°C |

| Voltage at any other pin · · · · · · -0.3V to Vcc +0.3V | (Military) · · · · · -55°C to +125°C                             |

| DC Current Drain per input pin · · · · · · · · 10mA     | Storage Temperature Range:                                       |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

Vcc = 5V ±5%, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

| PARAMETI                                               | ER                                                   | SYMBOL             | CONDITIONS                                                              |                      | LIMITS             |                     | UNIT           |

|--------------------------------------------------------|------------------------------------------------------|--------------------|-------------------------------------------------------------------------|----------------------|--------------------|---------------------|----------------|

|                                                        |                                                      |                    |                                                                         | MIN                  | TYP                | MAX                 |                |

| ARINC INPUTS - 429DI1 (A),                             | 429DI1 (B), 429DI2 (A) & 429D                        | I2 (B)             |                                                                         |                      |                    |                     |                |

| Differential Input Voltage:                            | ONE<br>ZERO<br>NULL                                  | VIH<br>VIL<br>VNUL | ARINC Input Pins: Common mode voltage less than ±5V with respect to GND | 6.5<br>-13.0<br>-2.5 | 10.0<br>-10.0<br>0 | 13.0<br>-6.5<br>2.5 | V<br>V         |

| Input Resistance:                                      | Differential<br>To GND<br>To Vcc                     | Rı<br>Rg<br>Rh     |                                                                         | 12<br>12<br>12       | 27<br>27           |                     | KΩ<br>KΩ<br>KΩ |

| Input Current:                                         | Input Sink<br>Input Source                           | lıн<br>lıL         |                                                                         | -450                 |                    | 200                 | μA<br>μA       |

| Input Capacitance:<br>(Guaranteed but not tested)      | Differential<br>To GND<br>To Vcc                     | Cı<br>Cg<br>Ch     | Pins 2 to 3, 4 to 5                                                     |                      |                    | 20<br>20<br>20      | pF<br>pF<br>pF |

| BI-DIRECTIONAL INPUTS - BD                             | 00 through BD15                                      |                    |                                                                         |                      |                    |                     |                |

| Input Voltage:                                         | Input Voltage HI<br>Input Voltage LO                 | VIH<br>VIL         |                                                                         | 2.1                  |                    | 0.7                 | V              |

| Input Current:                                         | Input Sink<br>Input Source                           | lıн<br>lıL         |                                                                         | -1.5                 |                    | 1.5                 | μA<br>μA       |

| ALL OTHER INPUTS - SEL, EN                             | 1, EN2, PL1, PL2, ENTX, CWS                          | ΓR, CLK & Μ        | ĪR                                                                      |                      |                    |                     |                |

| Input Voltage:                                         | Input Voltage HI<br>Input Voltage LO                 | VIH<br>VIL         |                                                                         | 3.5                  |                    | 0.7                 | V              |

| Input Current:                                         | Input Sink<br>Input Source                           | lıн<br>lıL         |                                                                         | -20                  |                    | 10                  | μA<br>μA       |

| OUTPUTS - $\overline{D/R1}$ , $\overline{D/R2}$ , BD00 | through BD15, TX/R, 429DO, 4                         | 29DO & TX          | CLK                                                                     |                      |                    |                     |                |

| Output Voltage:                                        | Logic "1" Output Voltage<br>Logic "0" Output Voltage | Voh<br>Vol         | Iон = -1.5mA<br>IoL = 2.6mA                                             | 2.7                  |                    | 0.4                 | V              |

| Output Current:<br>(Bi-directional Pins)               | Output Sink<br>Output Source                         | loь<br>loн         | Vout = 0.4V<br>Vout = Vcc - 0.4V                                        | 3.0<br>1.1           |                    |                     | mA<br>mA       |

| Output Current:<br>(All Other Outputs)                 | Output Sink<br>Output Source                         | loь<br>loн         | Vout = 0.4V<br>Vout = Vcc - 0.4V                                        | 2.6<br>1.1           |                    |                     | mA<br>mA       |

| Output Capacitance:                                    |                                                      | Co                 |                                                                         |                      |                    | 15                  | pF             |

| SUPPLY INPUT - Vcc                                     |                                                      |                    |                                                                         |                      |                    |                     |                |

| Standby Supply Current:                                |                                                      | Icc1               |                                                                         |                      |                    | 20                  | mA             |

| Operating Supply Current:                              |                                                      | Icc2               |                                                                         |                      |                    | 20                  | mA             |

# **AC ELECTRICAL CHARACTERISTICS**

Vcc = 5V, GND = 0V, TA = Operating Temperature Range and fclk =  $1MHz \pm 0.1\%$  with 60/40 duty cycle

| DADAMETED                                                                                                  | OVMBOL                     |                 |     | LINUTO    |                |

|------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|-----|-----------|----------------|

| PARAMETER                                                                                                  | SYMBOL                     | MIN             | TYP | MAX       | UNITS          |

| CONTROL WORD TIMING                                                                                        |                            |                 |     |           |                |

| Pulse Width - CWSTR<br>Setup - DATA BUS Valid to CWSTR HIGH<br>Hold - CWSTR HIGH to DATA BUS Hi-Z          | tcwstr<br>tcwset<br>tcwhld | 130<br>130<br>0 |     |           | ns<br>ns<br>ns |

| RECEIVER TIMING                                                                                            |                            |                 |     |           |                |

| Delay - Start ARINC 32nd Bit to D/R LOW: High Speed<br>Low Speed                                           | tD/R<br>tD/R               |                 |     | 16<br>128 | μs<br>μs       |

| Delay - D/R LOW to EN L0W<br>Delay - EN LOW to D/R HIGH                                                    | td/ren<br>tend/r           | 0               |     | 200       | ns<br>ns       |

| Setup - SEL to <del>EN</del> L0W<br>Hold - SEL to <del>EN</del> HIGH                                       | tselen<br>tensel           | 20<br>20        |     |           | ns<br>ns       |

| Delay - EN LOW to DATA BUS Valid<br>Delay - EN HIGH to DATA BUS Hi-Z                                       | tendata<br>tdataen         |                 |     | 200<br>30 | ns<br>ns       |

| Pulse Width - EN1 or EN2<br>Spacing - EN HIGH to next EN L0W                                               | ten<br>tenen               | 200<br>50       |     |           | ns<br>ns       |

| FIFO TIMING                                                                                                |                            | <u> </u>        |     | •         |                |

| Pulse Width - PL1 or PL2                                                                                   | tpL                        | 200             |     |           | ns             |

| Setup - DATA BUS Valid to PL HIGH<br>Hold - PL HIGH to DATA BUS Hi-Z                                       | tDWSET<br>tDWHLD           | 110<br>10       |     |           | ns<br>ns       |

| Spacing - PL1 or PL2                                                                                       | tPL12                      | 0               |     |           | ns             |

| Delay - PL2 HIGH to TX/R LOW                                                                               | ttx/r                      |                 |     | 840       | ns             |

| TRANSMISSION TIMING                                                                                        |                            |                 |     |           |                |

| Spacing - PL2 HIGH to ENTX HIGH                                                                            | tpl2EN                     | 0               |     |           | μs             |

| Delay - ENTX HIGH to TXA(OUT) or TXB(OUT): High Speed Delay - ENTX HIGH to TXA(OUT) or TXB(OUT): Low Speed | tendat<br>tendat           |                 |     | 25<br>200 | µs<br>µs       |

| Delay - 32nd ARINC Bit to TX/R HIGH                                                                        | tDTX/R                     |                 |     | 400       | ns             |

| Spacing - TX/R HIGH to ENTX L0W                                                                            | tentx/R                    | 0               |     |           | ns             |

| REPEATER OPERATION TIMING                                                                                  |                            |                 |     |           |                |

| Delay - EN LOW to PL LOW                                                                                   | tenpl                      | 0               |     |           | ns             |

| Hold - PL HIGH to EN HIGH                                                                                  | tplen                      | 0               |     |           | ns             |

| Delay - TX/R LOW to ENTX HIGH                                                                              | ttx/ren                    | 0               |     |           | ns             |

| Master Reset Pulse Width                                                                                   | tmr                        | 200             |     |           | ns             |

| ARINC Data Rate and Bit Timing                                                                             |                            |                 |     | ± 1%      |                |

### **ADDITIONAL HI-8282A PIN CONFIGURATIONS**

(See page 1 for the 44-pin Plastic Quad Flat Pack)

## ORDERING INFORMATION

## HI - 8282A Cx x -xx (Ceramic)

| PART           | INPUT SERIES RESISTANCE |                     |  |  |  |  |

|----------------|-------------------------|---------------------|--|--|--|--|

| NUMBER         | BUILT-IN                | REQUIRED EXTERNALLY |  |  |  |  |

| No dash number | 35 Kohm                 | 0                   |  |  |  |  |

| -10 (Note 1)   | 25 Kohm                 | 10 Kohm             |  |  |  |  |

| PART<br>NUMBER | TEMPERATURE<br>RANGE | FLOW | BURN<br>IN | LEAD<br>FINISH              |

|----------------|----------------------|------|------------|-----------------------------|

| ı              | -40°C TO +85°C       | I    | NO         | Gold                        |

| Т              | -55°C TO +125°C      | Т    | NO         | Gold                        |

| M              | -55°C TO +125°C      | М    | YES        | Tin / Lead (Sn / Pb) Solder |

| PART<br>NUMBER | PACKAGE<br>DESCRIPTION               |  |

|----------------|--------------------------------------|--|

| CD             | 40 PIN CERAMIC SIDE BRAZED DIP       |  |

| CJ             | 44 PIN J-LEAD CERQUAD                |  |

| CL             | 44 PIN CERAMIC LEADLESS CHIP CARRIER |  |

# HI - 8282A Px x x -xx (Plastic)

| PART           | INPUT SERIES RESISTANCE |                     |  |

|----------------|-------------------------|---------------------|--|

| NUMBER         | BUILT-IN                | REQUIRED EXTERNALLY |  |

| No dash number | 35 Kohm                 | 0                   |  |

| -10 (Note 1)   | 25 Kohm                 | 10 Kohm             |  |

| PART<br>NUMBER | LEAD<br>FINISH                           |  |

|----------------|------------------------------------------|--|

| Blank          | Tin / Lead (Sn / Pb) Solder              |  |

| F              | 100% Matte Tin (Pb-free, RoHS compliant) |  |

| - | PART<br>NUMBER | TEMPERATURE<br>RANGE | FLOW | BURN<br>IN |

|---|----------------|----------------------|------|------------|

|   | I              | -40°C TO +85°C       | I    | NO         |

|   | Т              | -55°C TO +125°C      | Т    | NO         |

| 1 | М              | -55°C TO +125°C      | М    | YES        |

| PART<br>NUMBER | PACKAGE<br>DESCRIPTION                 |  |

|----------------|----------------------------------------|--|

| PJ             | 44 PIN PLASTIC J-LEAD PLCC (Note 2)    |  |

| PQ             | 44 PIN PLASTIC QUAD FLAT PACK (Note 2) |  |

#### NOTES:

- 1. The -10 configuration requires an external 10Kohm resistor in series with each ARINC input to guarantee specified voltage thresholds.

- 2. Both the 44-pin J-lead PLCC package and the 44-pin PQFP package are rated as Moisture Sensitivity Level (MSL) 1 and do not require special moisture handling precautions.

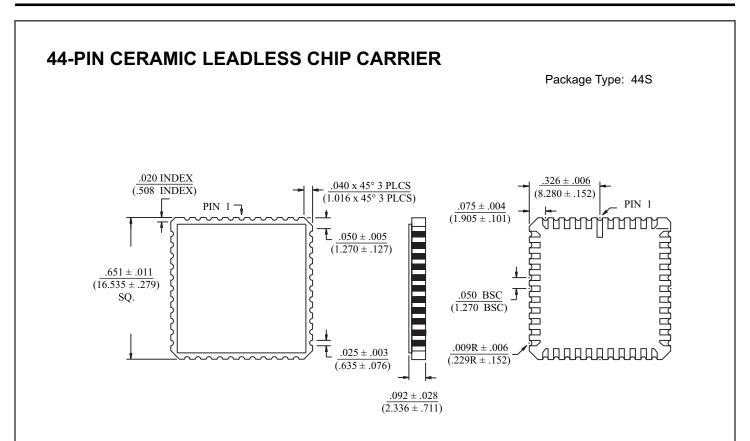

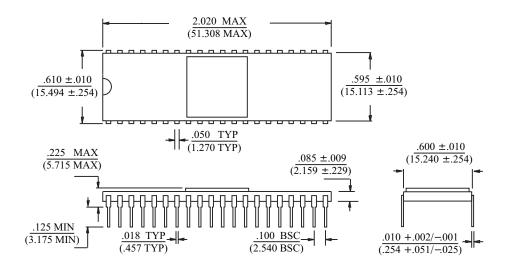

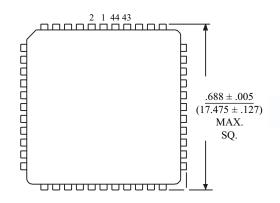

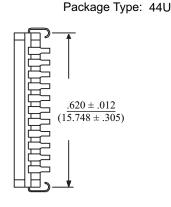

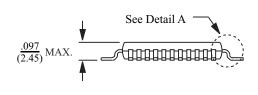

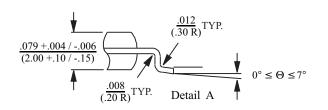

# HI-8282A PACKAGE DIMENSIONS

inches (millimeters)

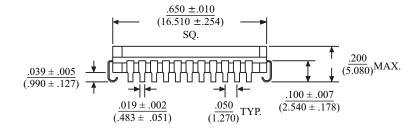

### 40-PIN CERAMIC SIDE-BRAZED DIP

Package Type: 40C

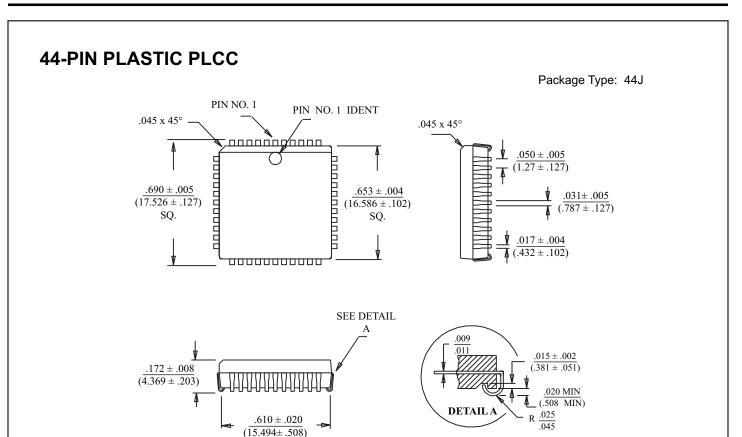

### 44-PIN J-LEAD CERQUAD

# HI-8282A PACKAGE DIMENSIONS

inches (millimeters)

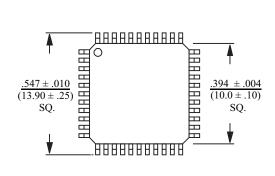

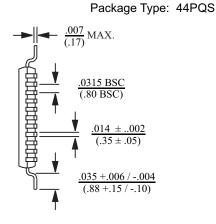

## 44-PIN PLASTIC QUAD FLAT PACK (PQFP)

# **HI-8282A PACKAGE DIMENSIONS**

inches (millimeters)